InfiniBand Link Layer Cores

InfiniBand Link Layer Cores

Polybus offers a family of InfiniBand Link Layer Cores ranging from a Single Data Rate 4X core (1 GByte/Second) to a Quad Data Rate 4X core (4Gbytes/second) for FPGAs and a Quad Data Rate 8X core (8 GBytes/scond) for ASICs. All Link Layer cores are available for both Xilinx and Altera FPGAs as well as for ASIC applications.

There are three members of the Link Layer family. The SDR Link Layer Core is the smallest core, it operates at 125 MHz and supports bidirectional speeds of 10GBits/second in each direction. Customers are currently using the SDR core in Xilinx Virtex2P, Xilinx Virtex4FX, Xilinx Virtex5. Altera Stratix2GX and ASICs. The SDR core can operate in the lowest speed grades of the Virtex4FX (-10) and the Stratix2GX (-5).

The DDR (Double Data Rate) Link Layer Core operates at 250 MHz and supports bidirectional speeds of 20GBits/second. The DDR core requires a 5 GHz SerDes. Customers are using the DDR core in Xilinx Virtex4FX, Virtex5 and Kintex7, Altera Stratix2GX and in ASICs. The DDR core requires the middle speed grades of the the Virtex4FX (-11) and the Stratix2GX (-4).

The QDR (Quad Data Rate) Link Layer Core operates at 500MHz in ASICs and 250MHz in FPGAs. In ASICs the QDR core supports 1X, 4X and 8X QDR (80G) operation. In FPGAs the core supports 1X and 4X QDR operation or 8X DDR operation (40G). The QDR core includes a PCS Layer that supports Altera Stratix5GX, Xilinx Kintex7 and Virtex7.

InfiniBand Transport Layer Cores

InfiniBand Transport Layer Cores

Polybus offers a family of InfiniBand Transport Layer Cores for use in Data Acquisition, High Performance Computing and Networking Applications. DDR and QDR UC Transport Layer cores support UC SEND and UC RDMA Write operations. The cores support from one to eight vritual lanes and 1024 Queue Pairs.

UC DDR and QDR TCAs

UC DDR and QDR TCAs

The TCAs combine a Transport Layer with a Link Layer to form a highly capable Target Channel Adapter. The TCAs operate at wire speed and very low latency. Data bandwidth for 4K packets on the QDR TCA is 3.95GBytes/Second at the user interface, packet rate is 59.45MPackets/second for 16 byte packets.

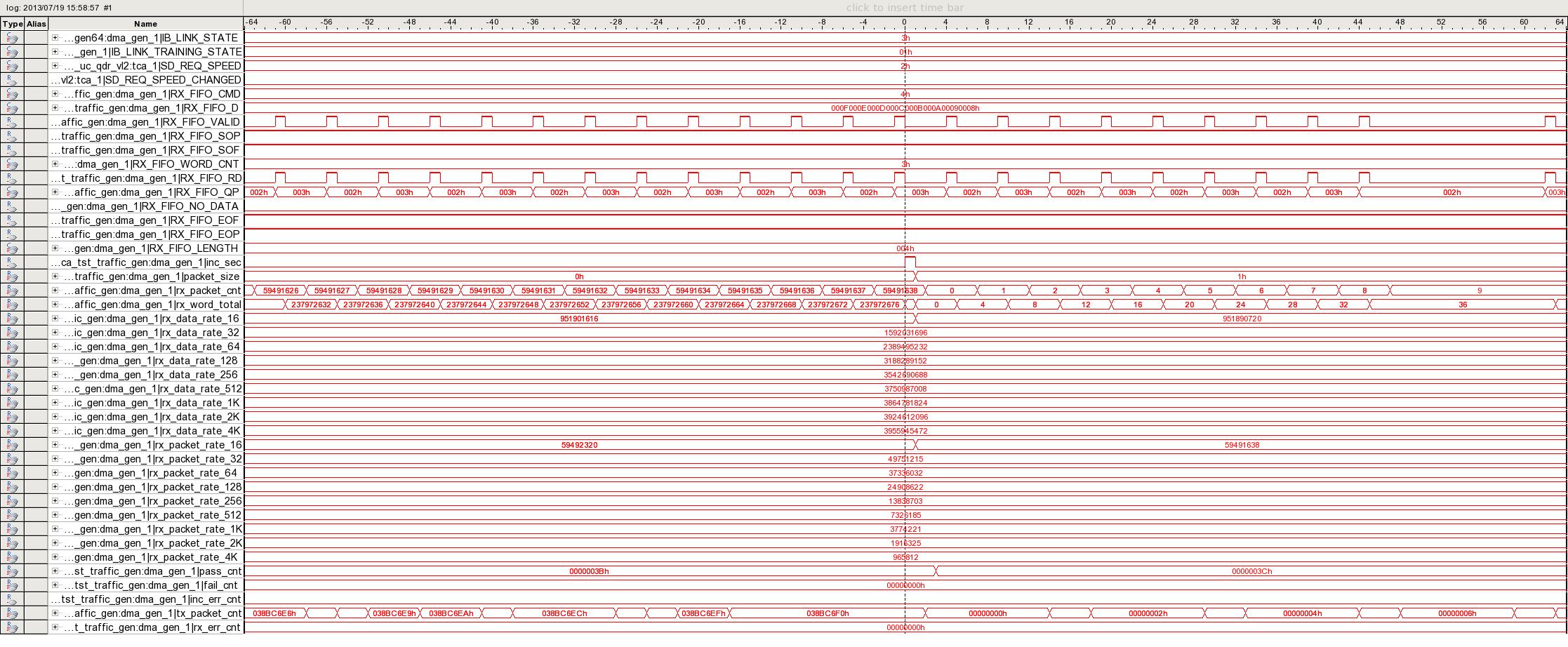

The snapshot below, taken from a running TCA on an FPGA, shows the data bandwidths and packets rates of the QDR TCA for packet sizes ranging from 16Bytes to 4KBytes. These are the delivered data rates after the IB headers have been stripped off and accounting for all IB overhead (flow control, skip sets and packet delimiters).

Applications

Applications

Target Channel Adapters and Bridges,

PCI -> InfiniBand

1G, 10G Ethernet -> InfiniBand

HyperTransport -> InfiniBand

SPI4 -> InfiniBand

FibreChannel -> InfiniBand

High speed data acquisition (Video, Radar ...)

Routers and Switches

More Information:

More Information:

Customization

Customization

Polybus will customize or extend the cores to meet client needs. In addition Polybus offers custom design and integration services.

For further information, datasheet, and pricing please contact

978 692-4828

(cell) 978 828-0944